Efficient Implementation of .AES Algorithm in FPGA Device

Keywords:

AES, Cryptography, Pipelining, Hardware architectures, VHDLAbstract

This paper presents an efficient FPGA implementation approach of the Advanced Encryption Standard (AES) Algorithm. The architectural optimization has been incorporated which include pipelining techniques. Speed is increased by proces ing multiple rounds simultaneously but at the cost of increased area. Algorithmic optimization techniques have also been used which include· exclusion of shift row stage and on the fly round key generation. The corresponding hardware reaJization is optimal in terms of area and offers high data throughout. n optimized code for the implementation of Rijndael algorithm for 128 bits has been developed and experimentally tested using Xilinx Virtex XC4VLX25 device. A 120.59 MHz clock frequency is achieved which translates to a throughput of 1.19 Gbps using 6323 Slice. The design handles both encryption and decryption and fits into a ingle FPGA.

Downloads

Downloads

Published

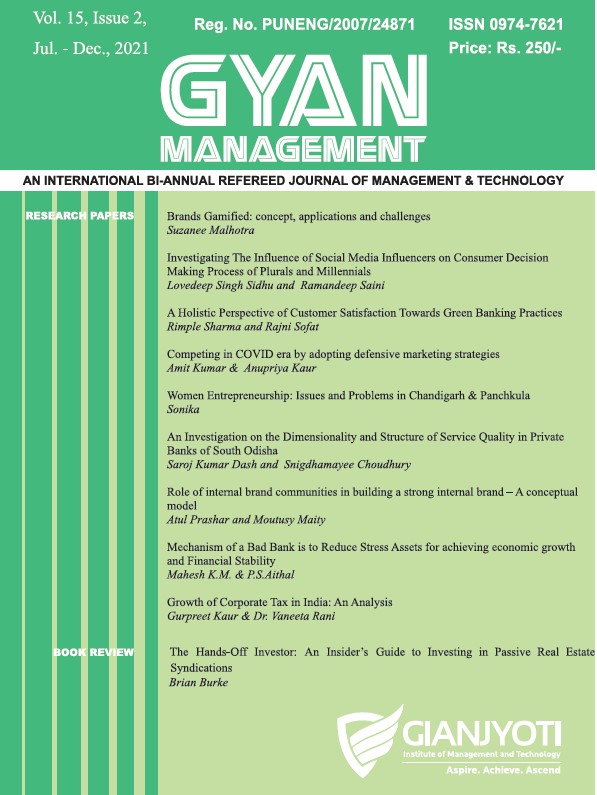

Issue

Section

License

Copyright (c) 2022 Gyan Management Journal

This work is licensed under a Creative Commons Attribution 4.0 International License.